TC 9-62

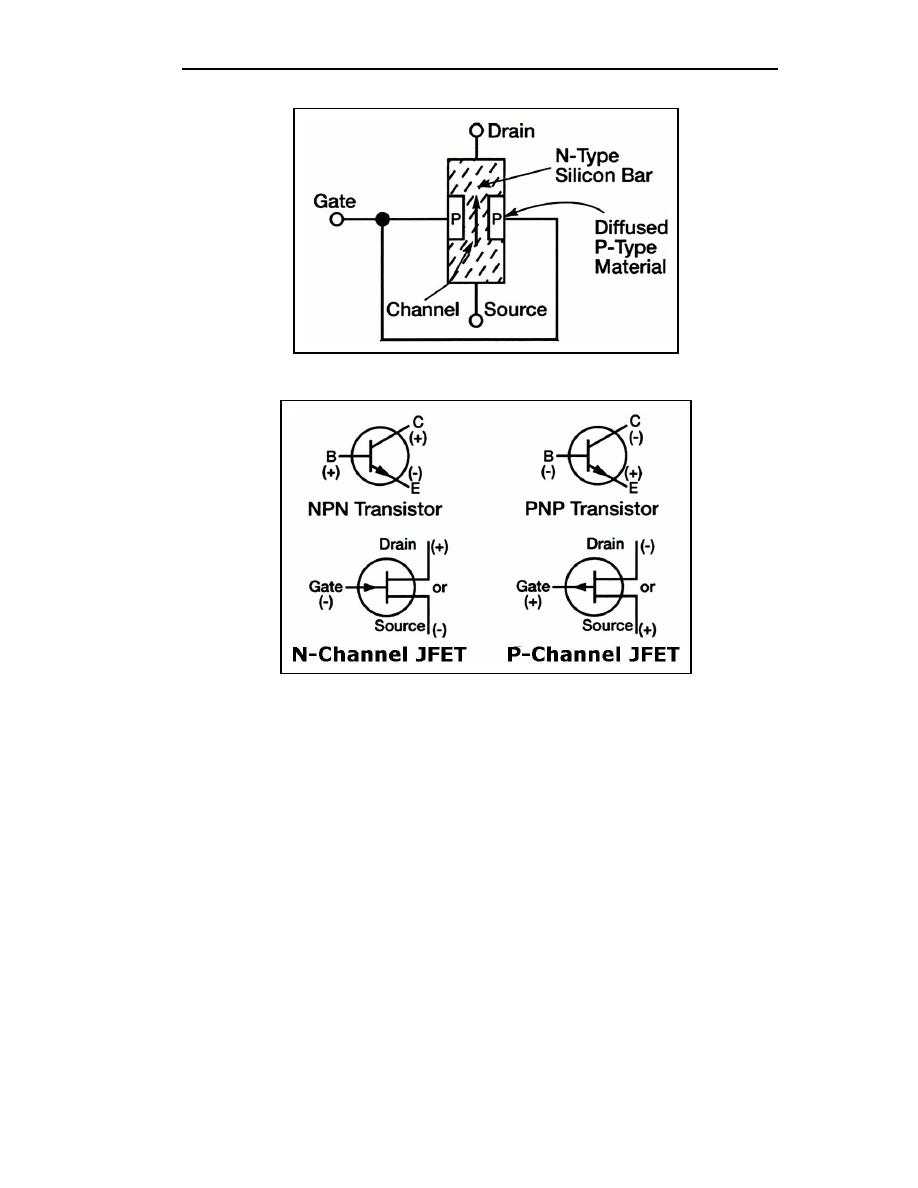

Figure 3-45. JFET Structure

Figure 3-46. Symbols and Bias Voltages for Transistors and JFET

3-78. Figure 3-47 shows how the JFET operates in a zero gate bias condition. Five volts

are applied across the JFET so that current flows through the bar from source to drain, as

indicated by the arrow. The gate terminal is tied to ground. This is a zero gate bias

condition. In this condition, a typical bar represents a resistance of about 500 ohms. A

milliammeter, connected in series with the drain lead and DC power, indicates the amount

of current flow. With a drain supply (VDD) of 5 volts, the milliammeter gives a drain

current (ID) reading of 10 milliamperes. The voltage and current subscript letters (VDD, ID)

used for a FET correspond to the elements of the FET just as they do for the elements of

transistors.

3-79. In Figure 3-48, a small reverse-bias voltage is applied to the gate of the JFET. A

gate-source voltage (VGG) of negative 1 volt applied to the P-type gate material causes the

junction between the P- and N-type material to become reverse biased. Just as it did in the

junction of the JFET. Since this region has a reduced number of current carriers, the effect

of reverse biasing is to reduce the effective cross-sectional area of the "channel." This

reduction in area increases the source-to-drain resistance of the device and decreases

current flow.

3-28

TC 9-62

23 June 2005

Previous Page

Previous Page